FERS-5200

Front-End Readout System

OVERVIEW

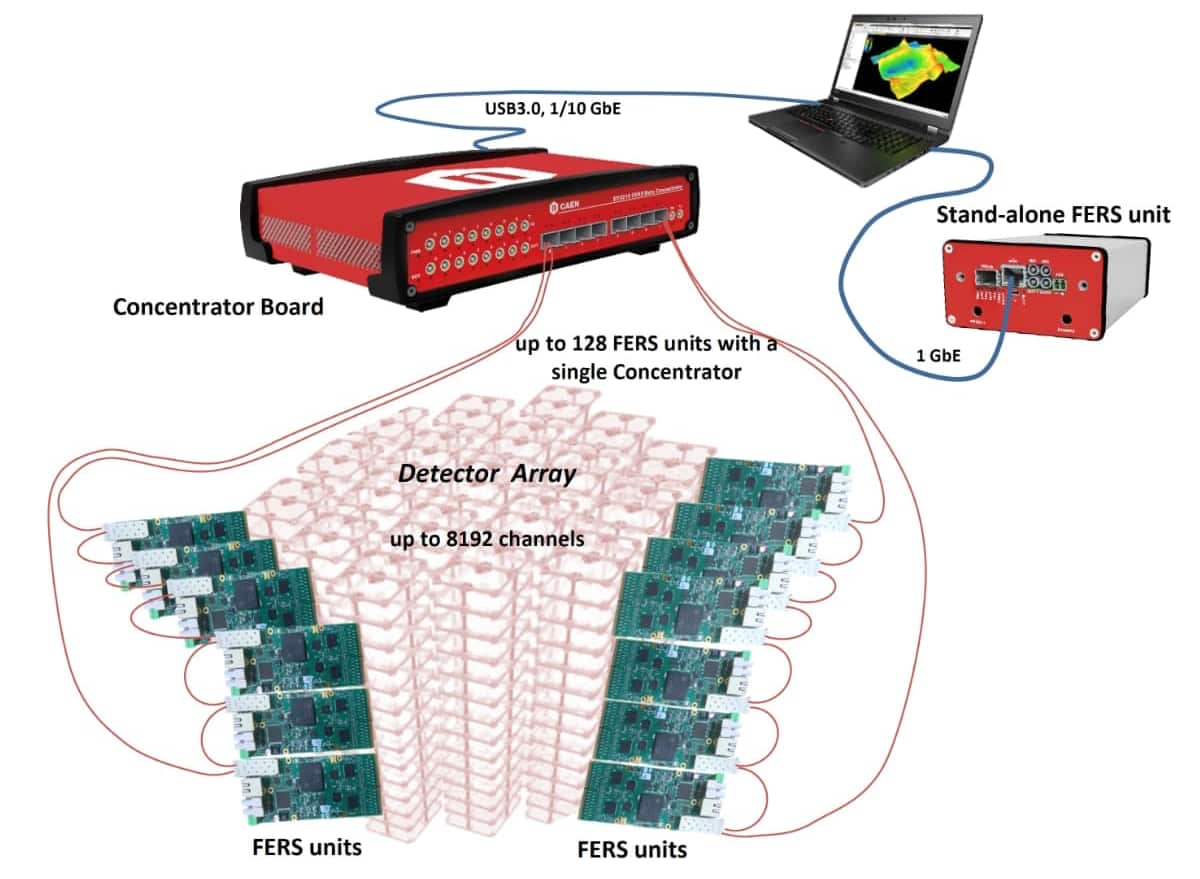

FERS-5200 is a Front-End Readout System designed for large detector arrays, such as SiPMs, multi-anode PMTs, Silicon Strip detectors, Wire Chambers, GEM, Gas Tubes and others.

FERS is a highly-scalable distributed platform. Each unit is a small card which houses 32 or 64 channels and includes Front End electronics, A/D converters, trigger logic, synchronization, local memory and readout interface.

FERS was designed with flexibility in mind: a single user-interface and readout infrastructure has been designed to support and perform a wide range of front-end tasks suitable for a large variety of detector types. In most cases, the front-end is based on ASIC chips. This design is perfect for large detector arrays, combining high density, cost-effective integration of multi-channel readout electronics with a small footprint and low power draw. The Front End ASIC can implement an analog chain made of preamplifier, shaper, peak sensing and discriminator: this is the case of the model A5202, based on the Citiroc-1A chip produced by Weeroc for SiPM readout (boxed version available). In other cases, the ASIC is a fast flash ADC (1 GS/s or more) that records the waveform of the input pulses and makes it possible to apply digital algorithms providing timing, energy and pulse shape information.